A tiny useful discovery about the 4046 phase locked loop chip

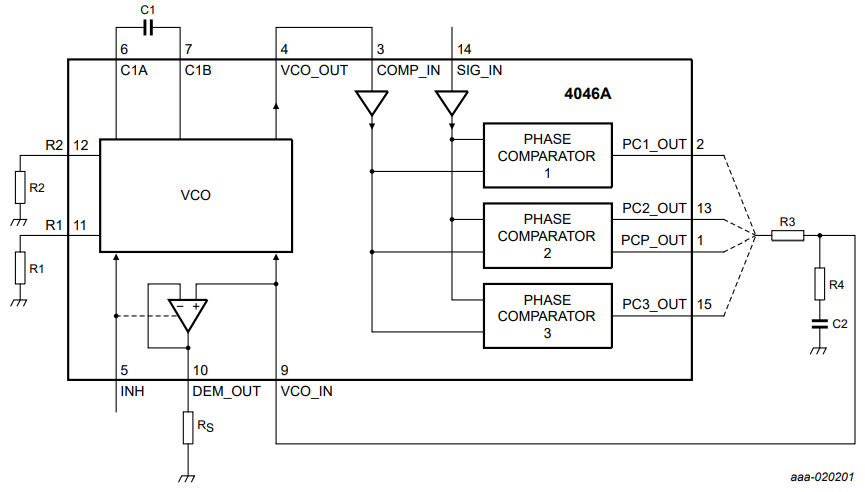

by Steve BushWhilst poring over 4046 phase locked loop data sheets, I noticed yet another subtle useful difference between the the later faster 74HC4046 (diag from NXP data sheet) and the earlier slower CD4046.

They both have the neat feature that the main phase detector signal input (SIG_IN) is both digital and analogue in that it can accept standard logic signals and also, if ac-coupled with a capacitor, the input self-biases into an amplifier that can work with signals of any waveform down to something like 400mV p-p.

But the 74HC4046 has a similar self-biasing amplifier on the other (COMP_IN) input to the phase detectors as well.

This means that if you have found something unusual to do within the loop, that cause a signal inversion at some point, then the two inputs of the detectors can be swapped to get the loop working, without loosing the useful built-in amplification.

The 74HC4046 also has a choice of three different phase detectors, compared with two in the CD4046.

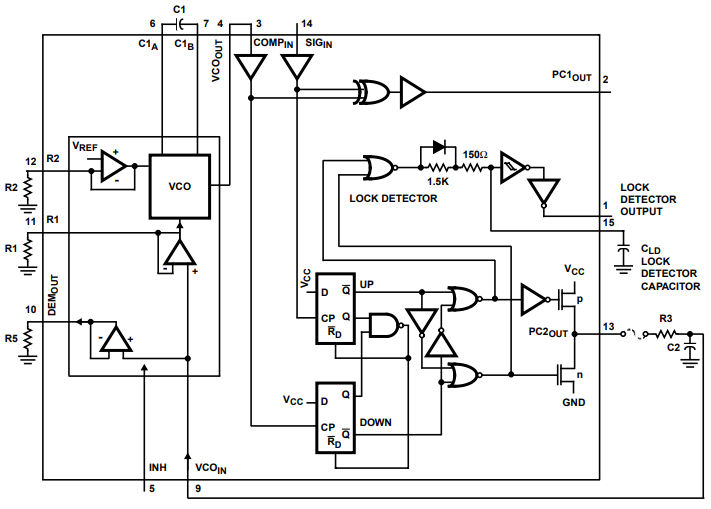

74HC7046 (daig from TI data sheet)

And on the subject of useful variants, both the ones above include a phase pulse output from the excellent and novel phase-frequency detector (phased detector II).

Then the 74HC7046 swaps that for a lock detector, although it has to loose phase detector 3 in the process to free-up a pin for the lock detector timing capacitor. The lock detector output is buffered.